На початку 2021 року почали з’являтися повідомлення про новий тип кеш-пам’яті, над яким працювала компанія AMD. В середині того ж року під час виставки Computex 2021 вона продемонструвала свою інновацію, яку назвали 3D V-Cache. Ця технологія дозволяє розміщувати значно більше кешу останнього рівня в вертикальному розташуванні, що зменшує зайняту площу на кристалі.

В даний час AMD вже презентує друге покоління 3D V-Cache, і на виставці CES 2026 компанія представила процесор Ryzen 7 9850X3D, підкресливши, що це найшвидший процесор для ігор у світі.

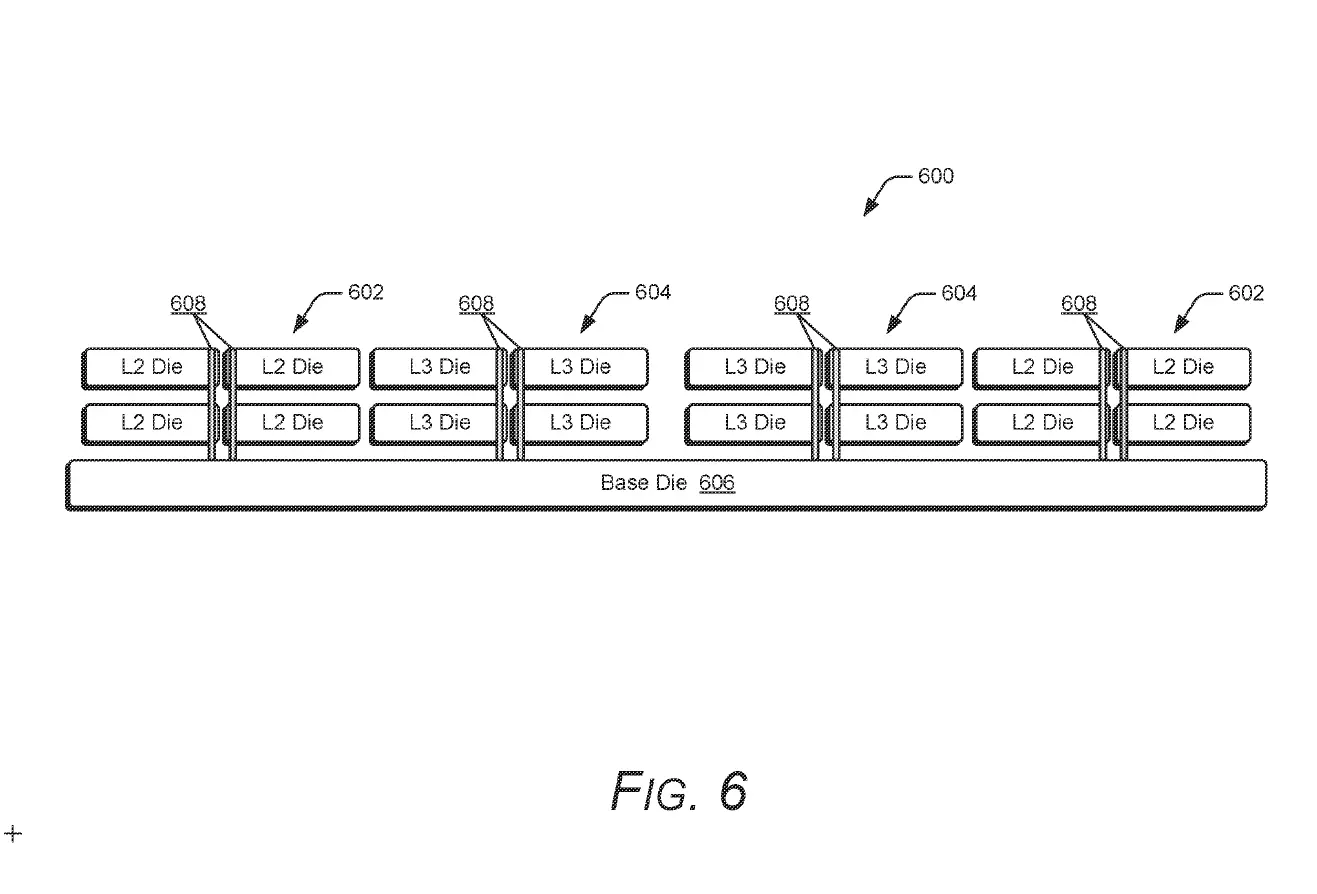

Згідно з архітектурою Zen, кеш останнього рівня відповідає L3, але новий патент свідчить про те, що AMD вирішила дослідити L2-кеш. Документ вказує, що компанія займається вертикальним стекуванням кешу цього рівня, намагаючись досягти вищої продуктивності та енергоефективності в майбутніх моделях Ryzen X3D.

AMD подала заявку на патент під назвою Balanced Latency Stacked Cache. Цей новий дизайн призначений для зменшення затримок при доступі до кеш-пам’яті та подальшого зменшення споживання енергії. У порівнянні з класичними процесорами, де не реалізовано 3D-кеш, традиційні конфігурації мають більші затримки та енергетичні витрати, що негативно впливає на швидкість роботи та ефективність пристрою.

В описі патенту зазначено, що нова конструкція 3D L2-кешу зменшує затримку доступу до стандартного L2-кешу обсягом 1 МБ з 14 до 12 тактів. Нехай на перший погляд це й виглядає незначно, в реальності, навіть кілька зекономлених тактів можуть суттєво впливати на загальну продуктивність і енергоефективність процесора. Для ілюстрації: типовий L2-кеш має затримку у межах 10–50 тактів, отже, заявлені показники виглядають вкрай конкурентоспроможно.

Патент також надає технічні деталі реалізації. Стековані чіпи з’єднуються за допомогою наскрізних кремнієвих з’єднань (TSV) або контактних переходів (BPV) для вертикального обміну даними між шарами. Ці з’єднання проходять через середину кристалів, що скорочує довжину сигнальних шляхів. Такий підхід формує симетричну, збалансовану структуру, яка забезпечує однорідний доступ до даних на всіх рівнях кешу. Саме це і є основною ідеєю Balanced Latency Stacked Cache.

При цьому варто зазначити, що патент все ще на стадії розгляду. Сам факт його подачі не означає, що технологія відразу з’явиться в серійних продуктах. Теоретичні основи не завжди точно реалізуються в реальних процесорах, тому остаточні результати залежать також від практичної реалізації.